Tagged RISC-V Processor

This thesis project aims to develop an instruction-set architecture (ISA), based on RISC-V, which tracks data types in the processor.

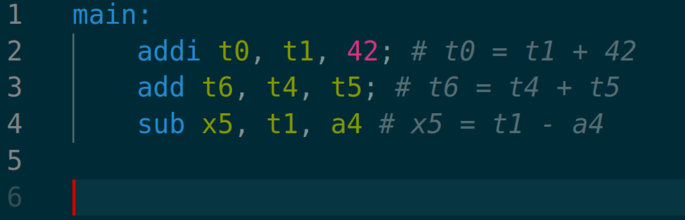

Contemporary ISAs do not track the data type of values in the processor. Instead, type-specific instructions are used to correctly handle the type of a value. For example, the multiply instruction in RISC-V has several variants to handle signed or unsigned integers of various sizes in addition to complementary instructions for multiplying floating-point values. This project will instead design an ISA that tracks data types in the processor itself, avoiding the need for type-specific instructions. This is meant to simplify the instructions set at minimal cost to the processor implementation. It might also increase performance.

This is a project best undertaken by 2 students, one with a focus on the hardware side (augmenting an open-source RISC-V processor for the new ISA), and one with a focus on compilers and the software side (making a simulator and augmenting an open-source RISC-V compiler to output the correct assembly). Tackling the hardware part first as a single person project is also possible.

A good project is also strongly expected to result in a published paper after the end of the thesis.

Please note that this thesis is carried out in collaboration with Emad Jacob Maroun from the Technical University of Denmark (DTU). The supervision and and the writing of the thesis will be done in English!

References

- Emad Jacob Maroun: “On Internally-Tagged Instruction Set Architectures”, https://www.techrxiv.org//1296562, https://doi.org/10.1109/LCA.2025.3585621

Contact

Oliver Keszöcze

Professor of Computer Engineering

TU Clausthal

E-Mail: oliver.keszoecze@tu-clausthal.de

Telephone: +49 5323 72-7153

Emad Jacob Maroun

Postdoctoral Researcher

Technical University of Denmark

E-Mail: ejama@dtu.dk