Volladdierer-Multiplizierer

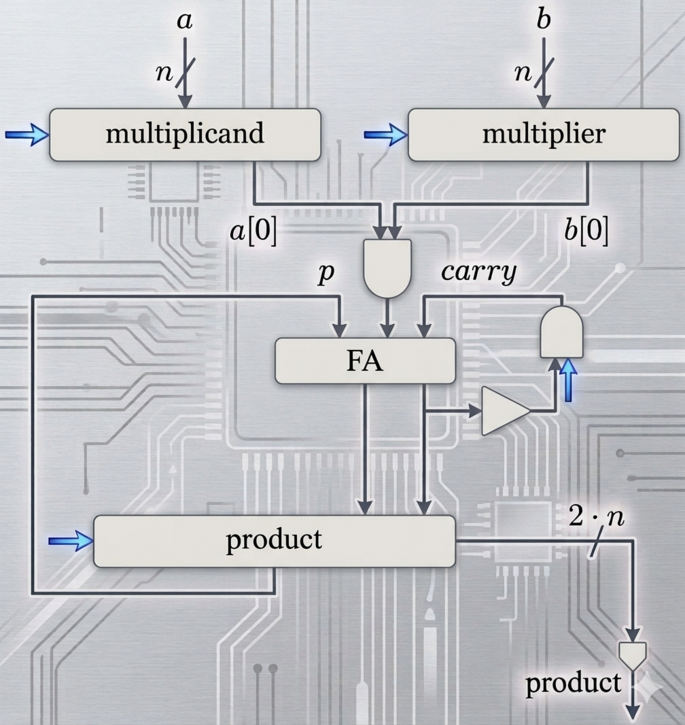

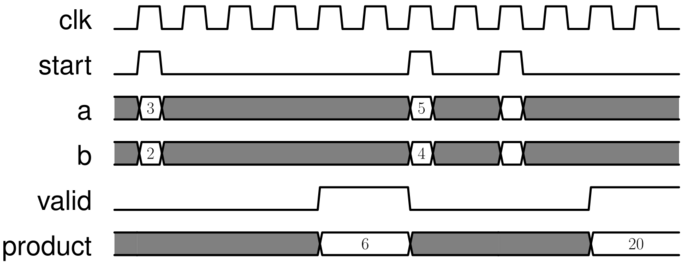

Die Abschlussarbeit befasst sich mit der Entwicklung und Implementierung eines seriellen n-Bit-Multiplizierers der aus lediglich einem einzigen Volladdierer besteht.

Der kontinuierlich steigende Energieverbrauch von Mikrochips stellt eine wachsende Herausforderung dar, sowohl in Bezug auf die Betriebskosten als auch die Umweltauswirkungen. Dies erfordert innovative Ansätze im Schaltungsdesign, um die Effizienz zu verbessern und den Strombedarf zu senken. Ein Multiplizierer, der aus lediglich einem Volladdierer besteht wird, auch wenn er langsamer rechnet, weniger Energie und Fläche benötigen.

Das Ziel der Arbeit ist es, einen solchen Multiplizierer zu entwickeln und zu evaluieren. Dies kann sowohl mittels Simulator als auch auf einem FPGA erfolgen. Die Implementierung sollte in einer modernen Hardware-Beschreibungssprache (Chisel oder Clash) erfolgen; VHDL/Verilog ist jedoch auch möglich.

Kontakt

Oliver Keszöcze

Professor für Technische Informatik

E-Mail: oliver.keszoecze@tu-clausthal.de

Telefon: +49 5323 72-7153