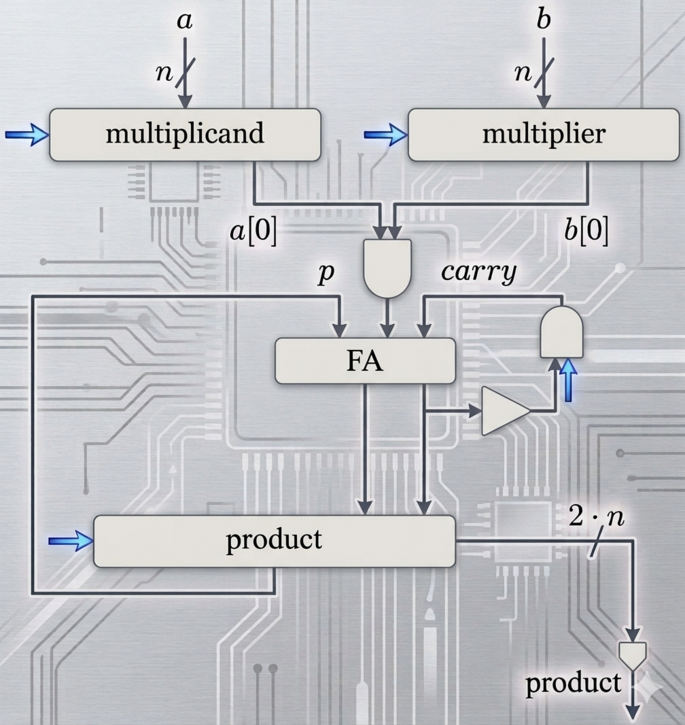

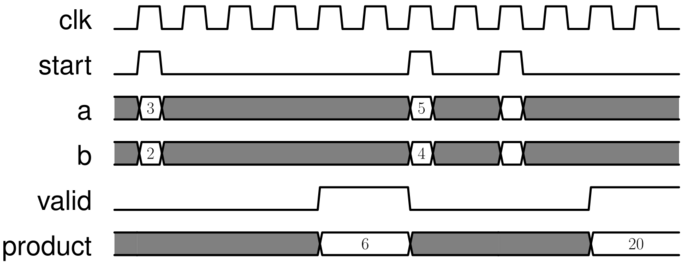

The thesis deals with the development and implementation of a serial n-bit multiplier consisting of a single full adder.

The continuously increasing energy consumption of microchips poses a growing challenge, both in terms of operating costs and environmental impact. This requires innovative approaches in circuit design to improve efficiency and reduce power consumption. A multiplier consisting of only one full adder, although slower, will require less power and area.

The aim of this work is to develop and evaluate such a multiplier. This can be done using a simulator or on an FPGA. The implementation should be done in a modern hardware description language (Chisel or Clash); however, VHDL/Verilog is also possible.

Contact

Oliver Keszöcze

Professor of Computer Engineering

E-Mail: oliver.keszoecze@tu-clausthal.de

Telefon: +49 5323 72-7153