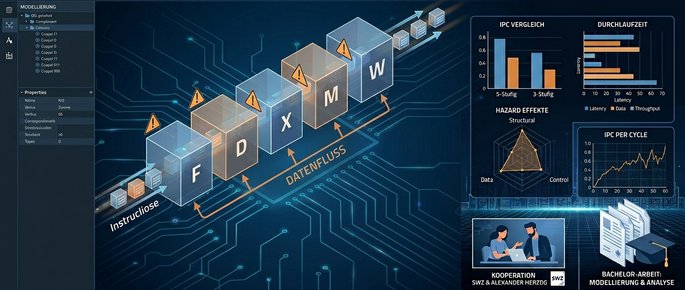

Modellierung und Leistungsanalyse von RISC-V-Pipeline-Architekturen mittels diskreter Ereignissimulation im Warteschlangensimulator

Hintergrund

Die Effizienz moderner Mikroprozessoren beruht maßgeblich auf dem Prinzip des Pipelinings, also der parallelen Verarbeitung verschiedener Befehlsphasen. Während die klassische RISC-Architektur häufig auf einer fünfstufigen Pipeline basiert, existieren alternative Ansätze wie dreistufige Pipelines. Um die Auswirkungen dieser Designentscheidungen auf den Durchsatz und die Latenz zu verstehen, ist eine abstrakte Modellierung auf Basis der Warteschlangentheorie ein wertvolles Werkzeug.

Zielsetzung der Arbeit

Das Ziel dieser Arbeit ist es, verschiedene Pipeline-Implementierungen eines RISC-V-Prozessors im Tool "Warteschlangensimulator" abzubilden. Dabei sollen die theoretischen Unterschiede zwischen einer klassischen fünfstufigen Architektur und einem dreistufigen Entwurf durch Simulation quantifiziert und analysiert werden.

Arbeitsschritte und Schwerpunkte

Der/die Studierende soll im Rahmen der Bearbeitung folgende Punkte bearbeiten:

- Theoretische Grundlagen:

- Einarbeitung in die RISC-V-Architektur.

- Analyse des Konzepts des Pipelinings sowie spezifischer Herausforderungen (Hazards, Stalls, Forwarding).

- Vergleich der theoretischen Konzepte einer klassischen fünfstufigen Pipeline (Fetch, Decode, Execute, Memory, Write-Back) mit einer dreistufigen Variante.

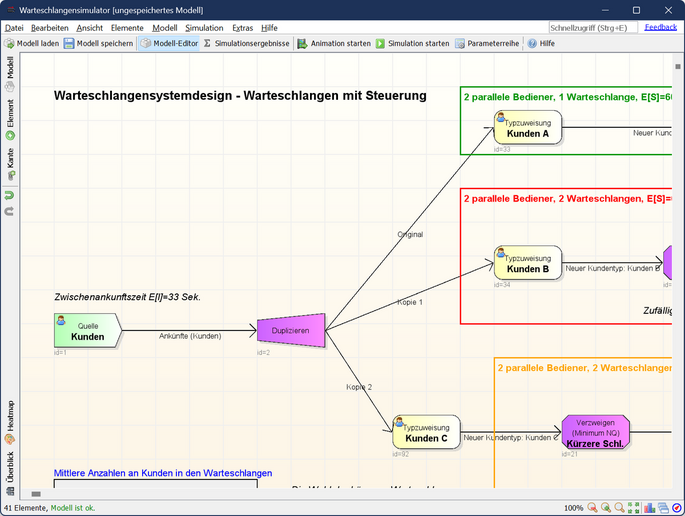

- Modellierung im Warteschlangensimulator:

- Abstraktion der Prozessorstufen als Bedienstationen innerhalb eines Warteschlangensystems.

- Erstellung eines Modells für die fünfstufige RISC-V-Pipeline.

- Entwicklung eines entsprechenden Modells für die dreistufige Pipeline.

- Simulation und Experimente:

- Definition von Lastprofilen (Befehlsmischverhältnissen), um unterschiedliche Programmszenarien zu simulieren.

- Durchführung von Simulationsläufen zur Ermittlung von Kenngrößen wie Auslastung, Durchlaufzeiten und Durchsatz (IPC - Instructions Per Cycle).

- Analyse und Evaluation:

- Gegenüberstellung der Simulationsergebnisse beider Architekturen.

- Diskussion der Vor- und Nachteile der dreistufigen gegenüber der fünfstufigen Pipeline hinsichtlich Performance und Komplexität.

Betreuung

Die Betreuung Arbeit erfolgt in Kooperation mit Alexander Herzog vom Simulationswissenschaftlichen Zentrum (SWZ), insbesondere im Hinblick auf die fachspezifische Nutzung und Konfiguration des Warteschlangensimulators.

Referenzen

- D. A. Patterson and J. L. Hennessy, Computer Organization and Design RISC-V Edition: The Hardware Software Interface, 2nd edition. Cambridge, MA: Morgan Kaufmann, 2021. ISBN: 978-0-12-820331-6

- M. Schoeberl, “Wildcat: Educational RISC-V Microprocessors,” in Architecture of Computing Systems. Springer Nature Switzerland, Oct. 2025, pp. 189–202. doi: 10.1007/978-3-032-03281-2_13.Available: www.jopdesign.com/doc/wildcat-arcs.pdf

- A. Herzog, Simulation mit dem Warteschlangensimulator: Mathematische Modellierung und Simulation von Produktions- und Logistikprozessen. Springer Fachmedien, 2021. doi: 10.1007/978-3-658-34668-3. ISBN: 978-3-658-34667-6A.

- Herzog and S. G, A-Herzog/Warteschlangensimulator: Warteschlangensimulator - Version 5.9. (Oct. 13, 2025). Zenodo. doi: 10.5281/zenodo.17337674. Available: zenodo.org/records/17337674

- “Warteschlangensimulation.” Available: www.simzentrum.de/forschungsprojekte/warteschlangensimulation

Kontakt

Oliver Keszöcze

Professor für Technische Informatik

E-Mail: oliver.keszoecze@tu-clausthal.de

Telefon: +49 5323 72-7153