Vorlesung: Verifikation und Test digitaler Systeme

Inhalt

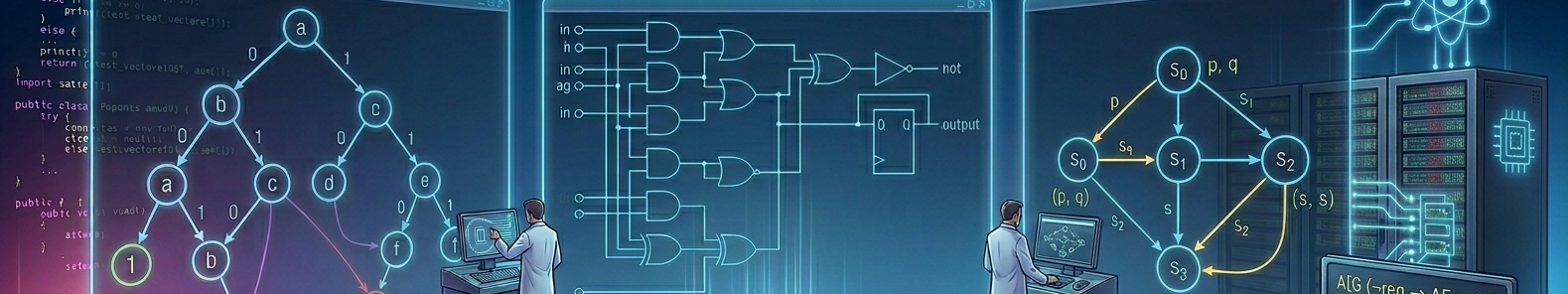

Für den Entwurf eines digitalen Systems werden heute in der Industrie ebenso viele Verifikationsingenieure wie Designer benötigt. Trotzdem beansprucht die Verifikation heute bereits 70%-80% der gesamten Entwurfszeit. Neben konventionellen Verifikationserfahren wie der Simulation sind werden seit einigen Jahren sogenannte formale Verifikationsmethoden in heutigen Entwursflüssen eingesetzt. Der Umgang mit diesen Methoden stellt ein wichtiges neues Aufgabenfeld dar. Im Gegensatz zur Simulation beruht die formale Verifikation auf exakten mathematischen Methoden zum Nachweis funktionaler Schaltungseigenschaften. Dadurch können Entwurfsfehler frühzeitiger und mit höherer Zuverlässigkeit als bisher erkannt werden. Jedes System zur formalen Hardwareverifikation erfordert:

Die Vorlesung behandelt diese drei Bereiche, vermittelt die grundlegenden Algorithmen und Konzepte moderner Werkzeuge für die formale Hardwareverifikation und erläutert deren Einsatz in der industriellen Praxis. Im Einzelnen werden in dieser Vorlesung die folgenden Punkte behandelt:

|

Literatur

- Vorlesungsfolien

- Haubelt, C., Teich, J., »Digitale Hardware/Software-Systeme: Spezifikation und Verifikation«, eXamen.press, 978-3-642-05355-9, kostenlos über die TU Clausthal online zu beziehen: link.springer.com/book/10.1007/978-3-642-05356-6